1.preview_dft

功能:在做inser_dft之前查测试点的信息,扫描链的信息。根据这些信息来确定所加的dft 规格是否完备。

一般是在规则写完并进行dft_drc之后,用此命令查看信息。最常用的就是默认的不带任何option的preview_dft,下面是一个preview_dft的报告。

****************************************

Preview_dft report

For : 'Insert_dft' command

Design : clk

Version: X-2005.09-SP4

Date : Fri Dec 12 09:55:48 2008

****************************************

Number of chains: 1

Scan methodology: full_scan

Scan style: multiplexed_flip_flop

Clock domain: mix_clocks

Scan enable: scan_en (no hookup pin)

Scan chain '1' (data_in[0] --> data_out[0]) contains 31 cells

************ Test Point Plan Report ************

Total number of test points : 1

Number of Autofix test points: 1

Number of Wrapper test points: 0

Number of test modes : 1

Number of test point enables : 0

Number of data sources : 1

Number of data sinks : 0

**************************************************

Dft signals:

TestData: clk_in (no hookup pin)

TestMode: test_en (no hookup pin)

最常用的还有preview_dft show all和preview_dft -test_points all

2.insert_dft

功能:将非扫描的触发器用扫描的触发器替代,添加额外的逻辑来提高fc(需启动autofix),执行增量编译来修复timing和DRC错误。

3.dft_drc -coverage_estimate

功能:执行DRC检查和测试覆盖率的分析,在insert_dft命令之后执行。下面是一个报告。

In mode: Internal_scan...

Design has scan chains in this mode

Design is scan routed

Post-DFT DRC enabled

Information: Starting test design rule checking. (TEST-222)

Loading test protocol

...basic checks...

...basic sequential cell checks...

...checking vector rules...

...checking clock rules...

...checking scan chain rules...

...checking scan compression rules...

...checking X-state rules...

...checking tristate rules...

...extracting scan details...

-----------------------------------------------------------------

DRC Report

Total violations: 0

-----------------------------------------------------------------

Test Design rule checking did not find violations

-----------------------------------------------------------------

Sequential Cell Report

0 out of 31 sequential cells have violations

-----------------------------------------------------------------

SEQUENTIAL CELLS WITHOUT VIOLATIONS * 31 cells are valid scan cells

Information: Test design rule checking completed. (TEST-123)

Running test coverage estimation...

1394 faults were added to fault list.

ATPG performed for stuck fault model using internal pattern source.

----------------------------------------------------------

#patterns #faults #ATPG faults test process stored detect/active red/au/abort coverage CPU time

--------- ------------- ------------ -------- --------

Begin deterministic ATPG:

#uncollapsed_faults=1099,

abort_limit=10... 0 1098 1 0/0/0 99.35% 0.02 0 1 0 0/0/0 99.42% 0.03

Pattern Summary Report

-----------------------------------------------

#internal patterns 0

-----------------------------------------------

Uncollapsed Stuck Fault Summary Report

-----------------------------------------------

fault class code #faults

------------------------------ ---- ---------

Detected DT 1372 Possibly detected PT 0 Undetectable UD 14 ATPG untestable AU

8 Not detected ND 0

test coverage 99.42%

-----------------------------------------------

Information: The test coverage above may be inferior than the real test coverage with customized protocol and test simulation library.

4.report_scan_configuration

功能:报告scan的配置信息

****************************************

Report : Scan configuration

Design : clk

Version: X-2005.09-SP4

Date : Fri Dec 12 12:47:49 2008

****************************************

========================================

TEST MODE: all_dft

VIEW : Specification

========================================

Chain count: 1

Scan Style: Multiplexed flip-flop

Maximum scan chain length: Undefined

Physical Partitioning: Horizontal

Replace: True

Preserve multibit segments: True

Clock mixing: Mix clocks

Internal clocks: none

Add lockup: TrueLockup

type: latchInsert

terminal lockup: False

Create dedicated scan out ports: False

Shared scan in: 0

Bidirectional mode: No bidirectional type

Minimize Hold Time Violations: False

Maximum Addtional Wire Length (%): Undefined

Test Clocks by System Clocks: False

Hierarchical Isolation: False

Multiple Scan Enable: Disable

Pipeline Scan Enable: Disable

Voltage Mixing: False

5.report_dft_signal

功能:报告由set_dft_signal设置的内容项,可以分成-view spec和-view existing_dft分着报

6.report_scan_path

功能:报告由set_scan_path指定的path和insert_dft插入的scan path。

选项:-view当指定spec的时候,报告set_scan_path指定的路径,当指定为existing_dft的时候,报告由insert_dft插入的scan path.

-chain指定报告的具体chain,如要报告所有的chain,使用all。

-cell报告指定chain的cell。

总结:

#write out scan reports

report_scan_configuration > reports/scan_config

report_dft_signal -view existing_dft > reports/dft_signals

report_scan_path -view existing_dft -chain all > reports/scan_chains

report_scan_path -view existing_dft -cell all > reports/scan_cells

#write out netlist and spf file for Tetramax

change_names -rules verilog -hier

set test_stil_netlist_format verilog

write -format ddc -hierarchy -output mapped_scan/RISC_CORE.ddc

write -f verilog -h -o tmax/RISC_CORE_SCAN.v

write_test_protocol -o tmax/RISC_CORE_SCAN.spf

上面标出了timing path最常用的七个属性,注意不能用get_object_name来对某条timing path在操作,因为timing path没有name的属性。只有具有name属性的单个对象的集合才可以使用get_object_name或者get_attribute XXX full_name。所以get_timing_paths要结合get_attribute使用。另外需要注意的是使用get_attribute得到的属性也有可能是一个集合,糊涂了是把。看看下面的例子:

上面标出了timing path最常用的七个属性,注意不能用get_object_name来对某条timing path在操作,因为timing path没有name的属性。只有具有name属性的单个对象的集合才可以使用get_object_name或者get_attribute XXX full_name。所以get_timing_paths要结合get_attribute使用。另外需要注意的是使用get_attribute得到的属性也有可能是一个集合,糊涂了是把。看看下面的例子:

DFT Compiler支持两种模式的带OCC的扫描链插入,一种是自身的设计已经带上OCC电路的,另一种是不带OCC电路的。

DFT Compiler支持两种模式的带OCC的扫描链插入,一种是自身的设计已经带上OCC电路的,另一种是不带OCC电路的。 假设需要的测试向量为7000个,则移位寄存器需要消耗的测试时间为7000*250000=1.75G cycle。假设测试时钟周期是100M,则需要耗时17.5s。需要消耗的memory为1.75G bit。很庞大,是把。怎么解决呢,容易想到的就是将这个扫描链的长度减小,用多个扫描链来替代,结构如下图:

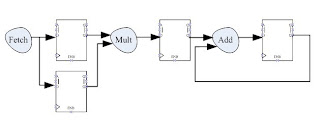

假设需要的测试向量为7000个,则移位寄存器需要消耗的测试时间为7000*250000=1.75G cycle。假设测试时钟周期是100M,则需要耗时17.5s。需要消耗的memory为1.75G bit。很庞大,是把。怎么解决呢,容易想到的就是将这个扫描链的长度减小,用多个扫描链来替代,结构如下图:  将这一个长的扫描链分解成1000个250个长度的扫描链,这样移位寄存器的load time就减少到以前的1/1000,但是付出的代价是测试管脚增加了太多,一方面芯片不可能提供这么多管脚做DFT,另外一般的ATE只有10到200个扫描信道,所以说上面的方案仍然需要改进。选取2500个寄存器做个一个扫描链的长度,这样就将扫描信道减小到100,就可以忍忍使用了。需要注意的是,这种并行的方法只是减少了数据的load的时间,数据量并没有减少。 能不能有一种方法能减少load time,同时又能减小pin和data volume的?illinois就是其中的一种方法。具体原理见下图:

将这一个长的扫描链分解成1000个250个长度的扫描链,这样移位寄存器的load time就减少到以前的1/1000,但是付出的代价是测试管脚增加了太多,一方面芯片不可能提供这么多管脚做DFT,另外一般的ATE只有10到200个扫描信道,所以说上面的方案仍然需要改进。选取2500个寄存器做个一个扫描链的长度,这样就将扫描信道减小到100,就可以忍忍使用了。需要注意的是,这种并行的方法只是减少了数据的load的时间,数据量并没有减少。 能不能有一种方法能减少load time,同时又能减小pin和data volume的?illinois就是其中的一种方法。具体原理见下图:

对于上面的与门,输入只会出现两种情况,一种就是000,一种就是111,不会出现其他的情况,这样就会减低故障覆盖率。这怎么办才好么?方法就是采用两种模式相结合的方式。下图:

对于上面的与门,输入只会出现两种情况,一种就是000,一种就是111,不会出现其他的情况,这样就会减低故障覆盖率。这怎么办才好么?方法就是采用两种模式相结合的方式。下图: 下面的几个图是说明使用illinois扫描结构效果的示意图:

下面的几个图是说明使用illinois扫描结构效果的示意图:

效果很好,但是有一个选择分组的问题,也就是说把哪些扫描链共享一个scan_in。分组的原则就是将对覆盖率的损害降到最低。

效果很好,但是有一个选择分组的问题,也就是说把哪些扫描链共享一个scan_in。分组的原则就是将对覆盖率的损害降到最低。